VHDL язык синтеза дискретных систем

Объясните значение слов и вы избавите мир от половины его заблуждений

Декарт

ИСТОРИЯ СОЗДАНИЯ VHDL

Традиционный подход к проектированию дискретных вычислительных систем (ДС) состоит в последовательном решении задач анализа и оптимизации некоторого начального варианта проектируемой ДС. Поэтому давней мечтой разработчиков ДС было создание единых средств описания ДС, которые позволяли бы решать задачи верификации и синтеза схем с различной степенью детальности их описания и, таким образом, объединять этапы проектирования в единый процесс нисходящего проектирования “сверху вниз”. Появление языка VHDL в определенной степени позволяет автоматизировать задачи проектирования от описания алгоритма функционирования ДС до реализации кристаллов микросхем. При этом понятие синтез следует определить как формализованный процесс построения схемы из некоторого заданного набора компонентов.

Языки описания аппаратуры (ЯОА/HDL - Hardware Digital Language) известны давно. Одним из первых более или менее удачных ЯОА был LOTIS - формальный язык, описывающий логические переменные и последовательностные схемы. Он разработан Шлэппи (IBM) в 1964 г. Затем в течение семидесятых годов в Европе и США было разработано много ЯОА, их насчитывалось более 200 - отечественных и зарубежных. Самыми известными являются МОДИС, МОДИС-В78, Автокод, МПЛ, ОСС-2, ФОРОС, EPICURE, CDL, DDL, ISPS, CONLAN, HILO, CASCADE, REGLAN и др.

Первой попыткой навести порядок в этом “столпотворении” было решение конференции по ЯОА о создании “языка согласия” CONLAN. Эта работа началась в 1976 г. и была успешно завершена созданием основ для “третьего поколения” (с полным семантическим определением) ЯОА. Одна из важнейших проблем, которую необходимо было решить, учитывая новую технологию параллельного проектирования, - обеспечение комплексного решения вопросов стандартизации, в том числе выработка стандартов на лингвистические средства спецификаций моделей проектов, протоколы и форматы обменных данных. Успех CONLAN послужил поводом для МО США в 1983 г. поддержать работы по созданию (на основе языка программирования Ада) нового языка спецификации проектов аппаратуры на базе сверхбольших высокоскоростных интегральных схем.

Разработка VHDL, завершенная в 1987 г., оказалась настолько успешной, что этот язык был принят в качестве стандарта ANSI/IEEE Std 1076-1987. Рестандартизация в IEEE проводится каждые пять лет, и на сегодня последней редакцией является VHDL’92, принятый в 1993 г. стандарт ANSI/IEEE Std 1076-1993. Об изменениях и дополнениях, появившихся в новой редакции языка VHDL, можно узнать из работы [1].

Концепции языков ЯОА до сих пор оставались “собственностью” тех небольших коллективов, которые либо непосредственно их создавали, либо использовали их при разработке уникальных электронных систем. С утверждением стандарта на VHDL любая разработка и документирование аппаратуры и алгоритмов функционирования ДС должны сопровождаться описанием на языке VHDL, т. е. VHDL-описание является неотъемлемой частью документации и для разработчика, и для заказчика.

ОСНОВНЫЕ СВОЙСТВА VHDL?

Одно из главных свойств - это способность описывать аппаратуру и ее работу во времени. Поэтому основными в VHDL являются такие близкие разработчику понятия, как объект проекта, интерфейс, порт, архитектура, сигнал, атрибуты сигнала, операторы параллельного присвоения, процесс и др.

Сигнал в VHDL трактуется весьма широко и может быть скалярным (целым, вещественным, битовым и т. д.) или векторным (шинным), булевым или многозначным. Многозначная (реально 5-, 9- или 12-значная) логика дает возможность выявлять с помощью моделирования такие явления в схемах, как гонки, неопределенности на выходах схем (например, асинхронного RS-триггера при запрещенных значениях входных сигналов), решать задачи мультиплексирования шины.

Свойства VHDL являются следствием (или результатом) особенностей реализации тех принципов, которые заложены в язык моделирования ДС.

ПРИНЦИПЫ МОДЕЛИРОВАНИЯ ДС И СРЕДСТВА VHDL

1. Событийное моделирование. Важнейшими в алгоритмах моделирования ДС являются:

- имитация реального времени;

- имитация параллельных процессов в однопроцессорной моделирующей ЭВМ.

Для организации моделирования во времени в VHDL применяется принцип событийного моделирования как наиболее эффективный по быстродействию. Его суть состоит в следующем:

- время в моделях представляется дискретным и может задаваться в диапазоне натуральных единиц времени от фемтосекунды (10-15 с) до часа;

- приращение времени на каждом шаге моделирования - величина переменная, равная интервалу времени между двумя последующими событиями (событием в моделях ДС называется любое изменение одного из сигналов в схеме).

2. Синхронизация параллельных процессов. Синхронизация параллельных процессов в VHDL обеспечивается:

- применением для сигналов специальных операторов параллельного присвоения “<=“, являющихся эквивалентами операторов присвоения “:=“ для простых переменных, но выполняемых на данном шаге моделирования с бесконечно малой дельта-задержкой. Например, при выполнении операторов

Y <= X1 and X2; (1)

Z <= not (X3 and Y); (2) происходит параллельное (через бесконечно малые дельта-задержки) присвоение вычисляемых значений сигналам Y и Z, так что в правой части оператора (2) будет использоваться не полученное в операторе (1), а старое значение Y, определенное ранее, например на предыдущем шаге моделирования во времени;

- использованием механизма процессов (PROCESS) и их запуска:

- с помощью сигналов активизации (два символа -- служат признаком комментария): process (X1,X2) -- процесс запускается только при изменении хотя бы одного из сигналов X1,X2 begin

Y <= not X1 and X2;

Z <= Y or X3; end process;

- с помощью оператора WAIT задержки процесса, который может располагаться в конце или в начале процесса: process process begin begin

Y <= not X1 and X2; WAIT ON X1,X2;

Z <= Y or X3; Y <= not X1 and X2;

WAIT ON X1,X2; Z <= Y or X3; end process; end process;

Оператор WAIT позволяет задавать достаточно сложные условия активизации процесса:

WAIT ON <список сигналов> UNTIL <условие> FOR время;

Например, для задания условия срабатывания схемы по фронту или по срезу (справа) сигнала С можно записать операторы

WAIT ON C UNTIL C=’1’;

WAIT ON C UNTIL C=’0’;

3. Использование механизма атрибутов. Атрибуты - это значения, связанные с поименованным объектом (сигналом, переменной), позволяющие более полно отображать свойства этих объектов (статические - переменных и динамические - сигналов). Наличие мощных средств атрибутов, а также средств имитации задержки WAIT, AFTER позволяет порождать многообразие моделей, имитирующих одни и те же свойства схемы, что дает возможность учитывать в VHDL-программах различные нюансы построения и работы цифровых схем. Так, то же условие срабатывания по фронту или по срезу С можно задать с помощью одного из выражений:

C’EVENT and C=’1’; not C’STABLE and C=’1’;

C’LAST_VALUE=’0’ and not C’STABLE;

C’EVENT and C=’0’; not C’STABLE and C=’0’;

C’LAST_VALUE=’1’ and not C’STABLE; где C’EVENT - атрибут типа Boolean, принимающий значение true, если с сигналом С произошло событие (сигнал С изменился); C’STABLE(T) - атрибут типа Boolean, принимающий значение true, если сигнал С стабилен в течение последних Т единиц времени (по умолчанию Т=0); C’LAST_VALUE - атрибут, определяющий значение сигнала С перед последним изменением этого сигнала.

Условие срабатывания схемы по фронту С и задержки переключения выходного сигнала Y на 15 нс можно записать в четырех вариантах:

Вариант 1

process

begin

WAIT ON C UNTIL C=’1’ FOR 15 ns;

Y <= not X1 and X2;

end process;

Вариант 2

process

begin

Y <= not X1 and X2;

WAIT ON CUNTIL C=’1’ FOR 15 ns;

end process;

Вариант 3

process (C)

if C=’1’ then

Y <= not X1 and X2 AFTER 15 ns;

endif;

end process;

Вариант 4

if C’EVENT and C=’1’ then

Y <= not X1 and X2 AFTER 15 ns;

endif;

4. Два типа моделей задержек распространения сигналов - инерционная и транспортная. Важными для описания работы реальных схем являются введенные в VHDL операторы задержки переключения сигналов:

3 инерционная задержка (по умолчанию);

3 транспортная задержка (сопровождается ключевым словом TRANSPORT).

Инерционная модель задержки разрешает переключение выходного сигнала Y только при условии, что длительность входных сигналов не меньше времени задержки, заданного после слова AFTER, т. е. инерционная задержка имитирует устойчивость схемы от высокочастотного “дребезга” на ее входе (в следующем примере длительностью менее 3 нс):

Y <= not X1 and X2 AFTER 3 ns;

Транспортная модель соответствует “чистой” задержке распространения: передается любой импульс, каким бы коротким он ни был. Так, оператор

Y <= TRANSPORT not X1 and X2 AFTER 15 ns; передает на Y с задержкой в 15 нс значения, соответствующие логическому выражению, независимо от частоты изменения этих значений.

5. Разнообразие форм описания объекта проекта. К замечательным свойствам VHDL, позволяющим использовать его для решения задач синтеза по методологии нисходящего проектирования, относится возможность описания объекта проекта с различной степенью детализации:

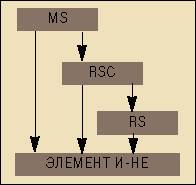

Рис.1. Иерархия моделей MS-триггера

- на поведенческом уровне с помощью двух форм:

- потоковой, имитирующей поведение объекта проекта как последовательность прохождения потока данных и сигналов управления;

- процессной, имитирующей поведение объекта проекта как совокупность независимых, но синхронизируемых во времени процессов, определяющих алгоритм функционирования;

- на структурном уровне имитирует объект проекта как совокупность компонентов структуры и связей между ними, при этом для описания компонентов может быть выбрана любая из перечисленных форм.

VHDL-ОПИСАНИЕ ОБЪЕКТА ПРОЕКТА

Полное описание VHDL-модели объекта проекта состоит из двух частей:

Рис.2. Логическая схема асинхронного RS-триггера

- описание интерфейса объекта проекта (ENTITY), включающее PORT (списки входных и выходных сигналов) и GENERIC (список задержек переключения и других констант);

- архитектура объекта проекта (ARCHITECTURE), включающая объявление переменных и дополнительных (внутренних) сигналов объекта проекта и операторную часть, описывающую объект проекта на структурном или поведенческом уровне.

VHDL-описание объекта проекта на структурном уровне должно включать и третью часть - описание конфигурации, задающей подключение библиотеки моделей типов элементов и выборку их в качестве компонентов структуры объекта проекта.

Количество уровней вложенности структурной модели произвольное, что позволяет фактически описать любую ДС от уровня ее устройств до уровня логических, принципиальных электрических схем и элементов и до кремниевого уровня.

Возможности создания иерархии структурных моделей рассмотрим на примере MS-триггера, который представляет собой совокупность двух последовательно включенных синхронных RS-триггеров, синхронный RS-триггер строится на основе асинхронного, а асинхронный - на элементах И-НЕ (рис. 1).

Элемент И-НЕ расположен на самом нижнем уровне иерархии. Поэтому для него единственно возможной архитектурой является поведенческая (выбираем процессную форму поведенческой модели):

-- МОДЕЛЬ И-НЕ

-- Интерфейс И-НЕ:

-- NAND2 - имя элемента,

-- time, bit - типы времени и сигналов,

-- Т - время переключения элемента entity NAND2 is generic (T:time:= 5 ns); port (X1,X2: in bit; Y: inout bit); end NAND2;

-- Архитектура (поведенческая процессная форма):

architecture POVED_NAND2 of NAND2 is begin process(X1,X2) begin Y <= not(X1 and X2) after T; end process; end POVED_NAND2;

-- МОДЕЛЬ АСИНХРОННОГО

RS-ТРИГГЕРА (рис. 2)

-- Интерфейс асинхронного RS-триггера: entity RS is

port(notS,notR: in bit; Q,NQ:

inout bit); end RS;

-- Архитектура (структурная форма):

architecture StrRS of

RS is component N2

-- задается интерфейс компонента

типа N2: port(X1,X2:in bit;Y:inout bit); end component; begin

-- указываются связи между компонентами С1, С2 структурной схемы RS-триггера:

C1: N2 port map(notS,NQ,Q);

C2: N2 port map(Q,notR,NQ); end StrRS;

В качестве компонента N2 может быть взят любой элемент, имеющий соответствующий интерфейс (например, элемент ИЛИ-НЕ - при смене элементной базы). Подстановка конкретных элементов задается конфигурацией архитектуры StrRS: library work; - подключение рабочей библиотеки и use work.all; - открытие всех элементов библиотеки для данной конфигурации configuration RSconf of RS is for StrRS

for C1: N2 use entity NAND2 (POVED_NAND2)

port map (X1,X2,Y)

end for;

for C2: N2 use entity NAND2 (POVED_NAND2)

port map (X1,X2,Y)

end for;

end for; end RSconf;

Аналогичным образом составляются модели синхронного RS-триггера (рис. 3) и MS-триггера (рис. 4):

-- МОДЕЛЬ СИНХРОННОГО RS-ТРИГГЕРА

-- Интерфейс синхронного

RS-триггера:

entity RSC is

port(S,C,R: in bit;Q,NQ: inout bit);

end RSC;

-- Архитектурное тело синхронного RS-триггера:

architecture StrRSC of RSC is component N2

- задается интерфейс компонента типа N2: port(X1,X2:in bit;Y:inout bit); end component;

- задается интерфейс компонента типа RScomp: component RScomp

port(notS,notR:in bit; Q,NQ: inout bit); end component; signal notS,notR: bit; - дополнительные сигналы введены для обозначения внутренних цепей; begin

-- указываются связи между компонентами С1, С2 структурной схемы RS-триггера:

C1: N2 port map(S,C,notS);

C2: N2 port map(C,R,notR);

C3: RScomp map(notS,notR,Q,NQ); end StrRS;

-- Конфигурация для архитектуры StrRSC: library work;

-- подключение рабочей библиотеки и use work.all;

-- открытие всех элементов библиотеки для данной конфигурации configuration RSCconf of RSC is for StrRSC

for C1: N2 use entity NAND2(POVED_NAND2)

port map (X1,X2,Y)

end for;

for C2: N2 use entity NAND2(POVED_NAND2)

port map (X1,X2,Y)

end for;

for C3: RScomp use configuration RSconf;

end for; end for; end RSCconf;

Компонент С3 связывается не с объектом RS, а с его конфигурацией, так как RS-триггер представлен структурной моделью, которая может иметь варианты архитектуры, задаваемые именно конфигурацией. Если С3 связать просто с объектом RS, то его внутренние компоненты окажутся не конкретизированными и модель будет неработоспособна.

-- МОДЕЛЬ MS-ТРИГГЕРА (рис. 4) entity MS is

port(S,C,R: in bit;Q,NQ: inout bit); end MS;

-- Архитектурное тело MS-триггера: architecture StrMS of MS is

component N2

-- задается интерфейс компонента типа N2:

port(X1,X2:in bit;Y:inout bit);

end component;

-- задается интерфейс компонента типа

RSCcomp:

component RSCcomp

port(S,C,R:in bit; Q,NQ: inout bit);

end component;

signal iS,iR,notC: bit; - дополнительные сигналы введены для обозначения внутренних цепей

begin

-- указываются связи между компонентами

С1, С2, C3 структурной схемы MS-триггера:

C1: RSCcomp port map(S,C,R,iS,iR);

C2: RSCcomp port map(iS,notC,iR,Q,NQ);

C3: N2 port map(C,C,notC);

end StrMS;

Рис.3. Логическая схема синхронного RS-триггера

Рис.4. Логическая схема MS-триггера

-- Конфигурация для архитектуры StrMS: library work; -- подключение рабочей библиотеки и use work.all; -- открытие всех элементов библиотеки для данной конфигурации configuration MSconf of MS is for StrMS

for C1: RSCcomp use configuration RSCconf;

end for;

for C2: RSCcomp use configuration RSCconf;

end for;

for C3: N2 use entity NAND2(POVED_NAND2)

port map (X1,X2,Y)

end for; end for; end MSconf;

Компоненты С1 и С2 связываются не с объектом, а с конфигурацией. При этом начинают действовать механизмы VHDL, обеспечивающие эффективное моделирование иерархических объектов: конфигурация RSCconf связывает компоненты С1 и С2 архитектуры StrRSC с конфигурацией RSconf, которая, в свою очередь, связывает свои компоненты С1 и С2 архитектуры StrRS с архитектурой POVED_NAND2 объекта NAND2. Таким образом объект MS и его составные части оказываются конкретизированными на всю глубину вплоть до элементной базы. При этом на каждом уровне проводится конкретизация компонентов только этого уровня, т. е. мы “не залезаем внутрь” компонентов этого уровня.

Рис.5. Прозрачный D-триггер, соответсвующий оператору IF...THEN...; VHDL-описание

Из приведенного примера видно, что конфигурация MS-триггера не связана напрямую с описанием его компонента - RSC-триггера, и поэтому в нее не потребуется вносить изменений при модификации этого компонента и тем более элементной базы. Следовательно, такое свойство VHDL позволяет организовать параллельные разработки моделей объекта проекта на различных уровнях иерархии, что может существенно сократить сроки исследования и создания объекта проекта в целом.

НЕКОТОРЫЕ ПРОБЛЕМЫ ПРИМЕНЕНИЯ VHDL В СИСТЕМАХ ПРОЕКТИРОВАНИЯ

Соответствие VHDL-описания и схемы. Важнейшим требованием к системе синтеза, строящейся на VHDL (система VHDL-синтеза), является установление соответствия между поведенческим описанием и реальной схемой, что приводит к ряду проблем из-за многоальтернативности решений и комбинаторной сложности этой задачи. Ниже приводятся простейшие примеры установления таких соответствий для комбинационных логических схем (КЛС) и схем с элементами памяти.

Логика любой КЛС, реализующей некоторую логическую функцию, описывается оператором параллельного присвоения:

Y <= not (X1 and X2) or (X3 X or X2);

Это соответствует асинхронной КЛС, в которой выход Y зависит только от информационных входов X1, X2, X3 (КЛС типа сумматор, асинхронные дешифратор и шифратор, схема выбора старшей “1” в коде и т. д.).

Асинхронные КЛС, имеющие, кроме информационных, адресные входы, определяющие выбор той или иной комбинации значений информационных входов (например, мультиплексор, демультиплексор и т. д.), а также синхронные КЛС следует описывать как PROCESS, который должен быть чувствительным ко всем входным сигналам, что задается параметрами процесса. Например, логическая схема мультиплексора может иметь такое VHDL-описание: process (A1,A2,D0,D1,D2,D3)

begin -- & - операция конкатенации

CASE (A1&A2) - => операция следования

WHEN “00” => Y<=D0;

WHEN “01” => Y<=D1;

WHEN “10” => Y<=D2;

WHEN “11” => Y<=D3;

end case; end process;

Условие синхронизации КЛС в VHDL-описании задается условным оператором IF..THEN..ELSE.., при этом все выходные сигналы КЛС должны быть определены полностью (не по умолчанию) всякий раз, когда процесс активизируется, т. е. альтернатива ELSE обязательна. Так, описанию process (A,B,C) begin

IF C=1 THEN Y <= A;

ELSE Y <= B;

end IF; end process; соответствует схема на рис. 5. Если же некоторый сигнал не присваивается (отсутствует ветвь ELSE в операторе IF), то подразумевается сохранение его старого состояния, что соответствует наличию в схеме элемента памяти типа триггера-защелки или прозрачного триггера (рис. 6): process (C,D)

begin

IF C=’1’ THEN Q <= D;

end IF; end process;

Системы VHDL-синтеза. В настоящее время существует большое число пакетов и систем проектирования, использующих VHDL. Одни из них относятся к промышленным (COMPASS, CADENCE, TANNER, SMASH, Mentor Graphics, Cadence, Workview Office), другие - к университетским (ALLIANCE, AMICAL, VANTAGE, SYNOPSYS). Характерным для них является применение методологии нисходящего проектирования, интерактивные средства моделирования с многооконным редактором, большой набор утилит, ориентированных на поддержку коллективной работы. Все они, как правило, работают под ОС UNIX и реализованы на станциях типа SUN и др.

Ряд систем (например, SYNOPSYS или система ХАСТ для разработки программируемых логических матриц фирмы Xilinx) позволяет разработчику выбирать, кроме VHDL, другие средства описания аппаратуры, например Verilog, синтаксической основой которого является язык Си. Практика показывает, что одной из наиболее надежных, быстродействующих и удобных в эксплуатации систем моделирования является система Vantage - среда моделирования на VHDL.

Рис.6. Комбинационная логическая схема, соотвествующая оператору IF...THEN...ELSE...; VHDL-описание

Очевидно, что ни один язык описания цифровой аппаратуры, в том числе и VHDL, не может полностью удовлетворить разработчика в части адекватного семантического отображения поведенческими моделями дискретных систем. Поэтому создаются системы, которые на базе подмножеств средств языка VHDL дополняют и расширяют функциональные и семантические возможности VHDL-конструкций в конкретных областях проектирования. Так, один из основных принципов разработки ДС - разделение на управляющую и операционную часть - не во всех ЯОА находит отражение. В VHDL некоторые операторы можно отнести к управлению (IF или CASE, а также защищенные назначения GUARDED assignments). Однако четкое разделение требует специальных языковых конструкций, однозначно отражающих функции управления. Такие конструкции предусмотрены в языке CASCADE. В работе [2] предложена композиция языков (CASCEDE и VHDL). Система Silicon 1076 [3] - САПР специализированных БИС, разрабатываемых по принципу параллельного проектирования, включает среду интерактивного архитектурного синтеза, для которого исходным является подмножество средств поведенческих VHDL-описаний. Система поддерживает многоцелевой синтезатор уровня регистровых передач, специализированные средства синтеза запоминающих и арифметических устройств.

В среде VHDL-синтеза все модели и средства, определяемые соответствующей методикой синтеза, включая пакеты (пакеты - средства задания уникальных, т. е. вводимых пользователем типов, подтипов, например единиц измерения, функций) и генераторы модулей, должны работать совместно. Следовательно, среда проектирования, основанная на VHDL, должна включать:

- поведенческое VHDL-описание проектируемой ДС;

- метод и средства декомпозиции поведенческого описания ДС (определяется методом синтеза и набором типовых элементов аппаратуры);

- набор поведенческих и/или структурных VHDL-описаний компонентов, соответствующих типовым элементам аппаратуры;

- правила выбора формы VHDL-описания компонента для его аппаратурной реализации.

Для успешного решения задач высокоуровневого синтеза с последующим переходом на более низкие уровни с использованием VHDL-описаний (VHDL-синтеза) должны выполняться следующие допущения:

1) генерируются схемы, функционирование которых адекватно VHDL-описаниям;

2) многообразие наборов VHDL-описаний в библиотеке компонентов для каждой аппаратной реализации соответствующей функции обеспечивает выбор оптимального варианта по заданному критерию синтеза схемы;

3) поведенческое VHDL-описание ДС, служащее входом для VHDL- синтеза, обычно не зависит от технологии изготовления системы, но для эффективных аппаратных решений следует учитывать технологическую информацию как можно раньше.

Как показывает опыт зарубежных и отечественных разработок, в настоящее время наиболее успешным оказывается применение поведенческих VHDL-моделей для синтеза устройств, последовательность обработки данных в которых может быть строго структурирована и представлена в виде схемы алгоритма или соответствующего потока сигналов. Тогда каждый блок алгоритма обработки, описываемый в виде процесса (VHDL-описания) однозначно реализуется соответствующими аппаратными средствами. Примерами могут быть спецвычислители, ориентированные на решение конкретного класса задач по определенному алгоритму, в частности устройство цифровой обработки сигналов [4].

Таким образом, для решения задач синтеза с применением языка VHDL в рамках САПР необходимо:

- создание библиотеки моделей поведенческого типа для проектируемых объектов в целом (для процессора - последовательность микроопераций для выполнения команд процессора);

- создание библиотеки моделей компонентов - конструктивных блоков разрабатываемого класса объектов (для процессора - АЛУ, наборы регистров, счетчики, мультиплексоры и т. д.);

- разработка процедуры синтеза с указанием связей между поведенческими и структурными моделями (для процессора процедура синтеза должна включать и критерии выбора длины слова, способов организации алгоритмов выполнения отдельной команды, например, умножения и т. д.)

Литература

1. Берже Ж. М. и др. VHDL’92. Новые свойства языка описания аппаратуры VHDL. Пер. с англ. М., Радио и связь. 1995.

2. Ле Фаоу К., Мермье Ж. Введение графов перехода языка CASCADE в язык VHDL. В кн.: VHDL для моделирования, синтеза и формальной верификации аппаратуры. Под ред. В. М. Михова. М., Радио и связь, 1995. С. 323 - 341.

3. Коттрелл Р. А. Проектирование специализированных БИС с помощью системы Silicon 1076. Там же. С.149 - 162.

4. Лундберг Л. Генерация VHDL-кода для моделирования и синтеза. Там же. С.163 - 177.

Александр Дорошенко