САПР

Корпорация Mentor Graphics недавно объявила о принципиально новом стратегическом направлении в области автоматизации проектирования электронных систем - проектировании “интегрированных систем”. Новая стратегия позволяет создать недостающие связи между существующими “островками” традиционной автоматизации проектирования и связать их в единый интегрированный процесс, начиная от структурного проектирования на системном уровне, разделения функций между программной и аппаратной частью системы и полной функциональной верификацией и кончая проектированием на физическом уровне. Проектирование интегрированных систем базируется на следующих ключевых принципах:

- анализ и верификация объекта на системном уровне;

- средства разработки встроенного ПО;

- совместное проектирование аппаратной и программной части объекта;

- повторное использование отработанных решений и обеспечение доступа к интеллектуальной собственности;

- интеграция всех этапов проектирования.

Mentor Graphics предлагает многоуровневый подход к анализу и верификации объекта на системном уровне. Проектирование кристаллов с плотностью до нескольких миллионов вентилей требует полной верификации на системном уровне. Новые средства верификации в сочетании с уже успешно использующимися на протяжении ряда лет средствами позволяют преодолеть это узкое место.

Новые средства включают Opnet Xpress Developer (OXD) - систему моделирования, дополняющую широко известную программу QuickHDL и основанную на обработке транзакций; QuickHDL-XLC - поцикловый оптимизатор для QuickHDL; SimExpress - систему аппаратной эмуляции.

Пакет OXD оперирует моделями, разработанными в среде Opnet Modeler (OM) фирмы Mil 3, являющейся графической программной оболочкой для моделирования и анализа коммуникационных и компьютерных систем. OM обеспечивает моделирование систем на уровне сетей, потоков данных и машин конечных состояний, ориентирован на проектирование телекоммуникационных и сетевых систем и включает возможность параллельного моделирования блоков системы на архитектурном и физическом уровне. Последнее достигается путем включения в общий интерфейс HDL-моделей аппаратных блоков, выполняющихся на QuickHDL. Таким образом аппаратные решения отрабатываются в системной среде на уровне протоколов передачи данных, управления очередями и других сложных системных процессов. Имеется возможность создания моделей программных блоков и средств связи в распределенных системах. Существенно ускоряется и делается более формализованным процесс генерации тестов.

Оптимизатор QuickHDL-XLC используется в качестве препроцессора для системы моделирования QuickHDL. Благодаря поцикловой оптимизации исходного HDL-файла процесс моделирования ускоряется в 10 - 50 раз за счет перекомпиляции кода, исполняемого затем на стандартном ядре QuickHDL. Поскольку поцикловое моделирование снижает затраты на обработку информации о временных задержках, обеспечивается 10 - 50-кратная экономия памяти в зависимости от степени асинхронности проекта. Возможно моделирование асинхронных узлов, схем многоуровневыми, в том числе многофазными, системами синхронизации, моделей на системном уровне. Используются такие усовершенствованные методы, как сокращение списка сигналов, многоярусные алгоритмы, обнаружение асинхронных циклов, поддержка драйверов с тремя и более состояниями, метод “черного ящика” и др. Входными данными могут служить списки цепей на вентильном уровне в форматах VHDL и Verilog.

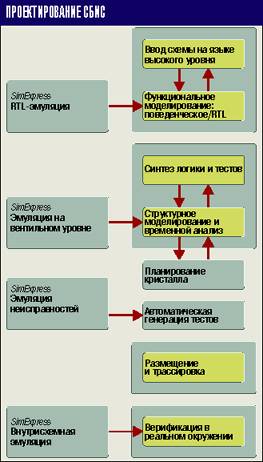

Система SimExpress обеспечивает аппаратную эмуляцию сложных схем (до 4 млн. вентилей) со скоростью от 0,5 до 20 МГц (до 1 млн. процессорных инструкций в секунду). Это позволяет полностью верифицировать системное и в значительной степени прикладное ПО сложнейших микропроцессоров и контроллеров, в том числе и в режиме интерактивной отладки, до этапа создания дорогостоящего прототипа. SimExpress использует заказные программируемые логические схемы с применением технологии “анализатор на кристалле”, благодаря чему достигается высокая скорость компиляции (350 тыс. логических вентилей в час - в десятки раз быстрее, чем у конкурирующих систем) и полная “прозрачность” схемы в режиме эмуляции. В случае очень больших проектов процесс компиляции может быть распараллелен на нескольких рабочих станциях. Подключение соответствующих средств автоматической генерации тестов дает возможность эмулировать неисправности.

Эмуляция схемы выполняется как на уровне регистровых передач (RTL), так и на вентильном уровне. С помощью дополнительной опции QuickHDL Express возможно совместное моделирование и эмуляция на языках Си, VHDL, Verilog и на RTL. Часть проекта, описанная, например, на языке Си, моделируется на поведенческом уровне программой QuickHDL, другая часть эмулируется на уровне RTL системой SimExpress. Исходной информацией для эмуляции является описание проекта на языках VHDL или Verilog. Возможен режим внутрисхемной эмуляции, которая реализует верификацию проектируемого кристалла в реальном окружении. Для внутрисхемной эмуляции используется полностью программируемый 6048-канальный двунаправленный интерфейс, обеспечивающий сопряжение с платами, использующими несколько асинхронных систем синхронизации. По сравнению с другими существующими системами аппаратной эмуляции, с учетом многократных итераций на этапе отладки скорость эмуляции увеличивается в 3 - 5 раз.

Другим важным направлением является параллельное/совместное проектирование аппаратной и программной части системы, которое в настоящее время особенно актуально для систем со встроенным ПО. Такие системы составляют основу современных телекоммуникационных систем, функционирующих по принципу распределенных сетей. Для них наиболее экономичным решением является использование локально встроенных программных блоков управления сетевыми протоколами, которое проще традиционного метода внешнего управления, заключающегося в адаптации ПО, выполняемого на специально выделенных узлах (рабочих станциях). Это позволяет сократить затраты на создание аппаратно-программных модулей управления при одновременном расширении их функциональных возможностей, например при добавлении голосовых, видео и других функций. Проектируя системы подобного типа, очень важно иметь возможность отладить программную часть проекта на так называемом “виртуальном прототипе”, не прибегая к созданию дорогостоящего аппаратного прототипа в кремнии.

Именно на такое проектирование ориентирован новый продукт фирмы Mentor Graphics - Seamless CVE (Co-Verification Environment). Seamless CVE позволяет не только отладить систему на ранних этапах проектирования, когда устранение ошибок не приводит к большим затратам, но и оптимизировать проект, вводя необходимые изменения, внесение которых на более поздних этапах либо невозможно, либо приводит к такому увеличению времени проектирования, при котором продукт безнадежно запаздывает с выходом на рынок. Для обеспечения всех функций программно-аппаратной отладки среда проектирования включает компилятор, отладчик исходного кода, просмотр содержимого регистров и памяти, окно просмотра принципиальной схемы, логический анализатор. Программы составляются на Си, Си++ и на языке ассемблера. Последнее позволяет верифицировать ОС реального времени и управление драйверами устройств в сочетании с программами более высокого уровня. Возможность управления оптимизацией со стороны пользователя позволяет существенно повысить производительность верификации путем выделения логического моделирования из программно-насыщенных операций, таких, как групповые обмены с памятью и алгоритмические подпрограммы.

Seamless CVE полностью интегрирован с другими системами логического моделирования, например с QuickSim II, QuickHDL, Verilog-XL, а также с системой аппаратной эмуляции SimExpress, что обеспечивает наибольшую эффективность отладки программного кода на ранних этапах проектирования. При этом не накладывается никаких ограничений ни на стиль проектирования, ни на возможности отладки ПО. Отладчики программного кода работают в знакомой им среде, получая в свое распоряжение всю мощь системы аппаратной эмуляции. Это позволяет, например, быстро выполнять анализ изменений типа “что, если?”. В настоящее время поддерживаются микропроцессорные модели Motorola 683XX, TMS3205X, Intel X86, ARM, PowerPC, Hitachi SuperH RISC Engine, Intel i960, ST10/20, STD950, NEC VR4300, V851, LSI LOGIC TinyRISC, TR4101 и др. Этот список предполагается значительно расширить. Типовая производительность составляет от 1000 до 10 000 команд в секунду.

Пожалуй, наиболее революционным фактором в стратегии проектирования “интегрированных систем” является появление на рынке электронных САПР понятия “интеллектуальная собственность”. До настоящего времени развитие электронной промышленности определялось в основном развитием технологии интегральных схем (ИС), которая обеспечивает удвоение числа транзисторов на кристалле каждые 18 месяцев. Инженеры-проектировщики логических схем, когда-то ограниченные предельными емкостями ИС, сейчас, с повсеместным переходом к субмикронной технологии, получили возможность воплотить на одном кристалле свои самые смелые мечты. Однако такое быстрое развитие технологии привело к резкому отставанию методологии и средств проектирования, которые в их сегодняшнем виде оказались не способны справиться с бескрайним океаном вентилей, оказавшихся в распоряжении проектировщиков. Так, используя современные средства проектирования, 75 инженерам-проектировщикам потребуется целый год, чтобы разработать функционально наполненную схему, состоящую из 50 млн. транзисторов. А именно такая плотность заполнения кристалла ожидается к 2000 г. Очевидно, что для проектов такого объема требуется существенное изменение подхода к проектированию, в основе которого лежит принцип повторного использования отлаженных проектных решений. Эти решения интегрируются в структуру разрабатываемой специализированной СБИС (сверхбольшой интегральной схемы) в виде ранее созданных крупных функциональных блоков, что позволяет проектировщикам сосредоточиться на разработке действительно инновационных решений, являющихся отличительной чертой (можно сказать, “товарным знаком”) проекта, выделяющей его на фоне конкурентов. Описания таких больших функциональных блоков в виде программных (soft cores), схемных (firm cores) или физических (hard cores) макросов концентрируют в себе понятие “интеллектуальной собственности”. Ожидаемый эффект от внедрения на рынок электронных САПР компонентов “интеллектуальной собственности” настолько велик, что фирма Mentor Graphics приняла решение создать специальное подразделение - Inventra IP Business Unit, ориентированное на разработку, накопление и распространение компонентов “интеллектуальной собственности”, а также на оказание услуг в области сопровождения процесса проектирования на базе вышеуказанных компонентов.

Каждый из трех названных типов макросов имеет свои преимущества и недостатки. Преимущества физических макросов (топологически привязанные блоки) заключаются в том, что они оптимизированы с точки зрения площади на кристалле, быстродействия и потребляемой мощности и характеризуются детерминированной задержкой распространения сигнала. К недостаткам можно отнести невозможность внесения изменений, а также привязанность к конкретным полупроводниковым фабрикам.

Схемные макросы представляют собой оптимизированные, легко синтезируемые списки цепей. Преимуществом таких макросов является то, что они могут быть дополнительно оптимизированы по быстродействию на завершающем этапе размещения и трассировки. Однако отсутствует возможность перераспределения функций с окружающей логикой с целью экономии площади кристалла.

Программные макросы поставляются в виде описаний на языке высокого уровня и обеспечивают наибольшую гибкость, так как могут быть синтезированы с использованием окружающей логики с оптимизацией по критерию быстродействие - площадь кристалла. Однако в этой гибкости заключается и их основной недостаток - вновь синтезируемые логические элементы должны быть верифицированы совместно с элементами, заимствованными из окружающей логики. Кроме того, возникает проблема стандартного для всей электронной промышленности интерфейса для обмена макросами. С этой целью в сентябре 1996 г. 35 ведущих компаний, производящих полупроводниковые приборы, вместе с поставщиками средств автоматизации проектирования и “интеллектуальной собственности” создали стандарт VSI (Virtual Socket Interface), который позволит в ближайшем будущем объединять на одном кристалле “виртуальные компоненты” от различных поставщиков.

В настоящее время наиболее развит рынок программных макросов. Так, список макросов, поставляемых фирмой Mentor Graphics, включает более 100 компонентов: процессоры, контроллеры периферии, DSP-функции, декодеры Рида - Соломона и Витерби, связные контроллеры и другие элементы. В комплект поставки программного макроса входят синтезируемая модель на языках VHDL или Verilog, средства “сопряжения” с программами синтеза, моделирования и тестирования, наборы тестовых векторов и описание типовых применений данного макроса с рекомендациями по использованию средств проектирования. Подразделение Inventra фирмы Mentor Graphics принимает также заказы на разработку программных макросов в соответствии со спецификацией заказчика.

Более того, Mentor Graphics недавно анонсировала принципиально новую бизнес-модель сотрудничества с фирмами - проектировщиками современных электронных систем. Модель основана на интегрированном подходе к проектированию специализированных БИС емкостью до 10 млн. вентилей, обеспечивающем интеграцию на одном кристалле нескольких макросов независимо от используемого пакета САПР. В настоящий момент модель проходит апробацию в рамках контракта с фирмой Telular, являющейся поставщиком телекоммуникационного оборудования для сотовых и беспроводных телефонов. В соответствии с контрактом необходимо обеспечить 70%-ное снижение стоимости проекта за счет замены существующих плат на несколько кристаллов СБИС. При этом специалисты Mentor Graphics интегрируют на одном кристалле несколько макросов, предлагаемых другими поставщиками, проводят тестирование проекта и поставляют его в виде, полностью готовом для массового производства.

Таким образом, сквозная ускоренная верификация проекта, распараллеливание моделирования и верификации программной и аппаратной части проекта и использование готовых решений, поставляемых в виде программных и аппаратных макросов “интеллектуальной собственности”, являются ключевыми моментами в новой стратегии проектирования интегрированных систем.

ПО корпорации Mentor Graphics поставляется фирмой “СКАН”, телефон: (095) 232-2343.

АНДРЕЙ ЛОХОВ

С автором статьи можно связаться по адресу: lokhov@scan.ru.

Используя современные средства проектирования, 75 инженерам-проектировщикам потребуется целый год, чтобы разработать функционально наполненную схему, состоящую из 50 млн. транзисторов